### **KPCI-3101 KPCI-3102 KPCI-3103 KPCI-3104**

# 225/400kHz, 12-Bit, Low Gain Analog I/O Boards

ftware

Our KPCI-3101/3102/3103/3104 multifunction boards provide strong performance at an extremely affordable price. Fully loaded, they are an attractive onestop solution, providing everything you need on a single low-cost board.

### **Functional Description**

This family of PCI-bus data acquisition boards features low gain, 12-bit resolution and a choice of throughput speeds. The KPCI-3101/3102 boards provide a throughput of 225kS/s, while the KPCI-3103/3104 are designed for applications requiring a faster input speed of 400kS/s. In addition, these multifunction boards include 32-bit DriverLINX software drivers, TestPoint drivers, and LabVIEW VIs. Keithley's new start-up software is also included at no charge.

### Analog Inputs

The analog inputs are software configurable for single-ended or differential inputs and bipolar or unipolar input ranges. An Amp Low connection allows single-ended inputs to be referenced to a common point other than ground to provide 16 pseudo-differential inputs. For added flexibility, a 1024-location channel-gain queue allows you to sample non-sequential channels and channels with different gains.

The Calibration utility allows both manual and automatic software calibrations.

### **Analog Input Acquisition Modes**

These boards can acquire a single value from any channel or a number of samples from multiple channels. To acquire data from multiple channels, the boards provide 2 scan modes: continuously paced and triggered. Both scan modes can be paced using an internal or an external clock.

The boards provide several triggering modes, including pre-trigger, post-trigger, and about-trigger modes.

- Pre-trigger mode allows acquisition to occur until an external trigger occurs.

- Post-trigger is the standard acquisition mode; acquisition begins after an internal or external trigger event and continues until an end condition occurs or the specified number of samples are collected.

- About-trigger mode allows acquisition to occur both before and after an external trigger.

#### Analog Outputs

The KPCI-3102 and -3014 boards feature 2 serial, multiplying, analog output channels. The output range is  $\pm 10V$  at 16-bit resolution. The analog outputs are set to 0V at power-up, and they supply single value updates suitable for DC control signals.

#### **Digital I/O**

All the boards feature 23 digital I/O lines. These lines are divided into two 8-bit ports and one 7-bit port. The ports are inputs by default, but can be software-configured for output. When used as outputs, they have sufficient capability to drive external solid-state relay modules (12mA sink and 15mA source).

The status of Ports A and B can be read at the rate of the analog input subsystem by including this special combined 16-bit digital channel in the analog input channel/gain list. When this 16-bit digital channel is the only channel in the channel/gain list, the rate can be increased to 3MHz.

The 7 bits of Port C can be written to at the speed of an analog input task that makes use of a channel/ gain list. Up to 1024 unique values can be written to the 7-bit port per analog input scan. The rate of the updates to Port C is limited to the speed of the analog input task.

#### Counter/Timers

These boards provide four 16-bit counter/timers. Uses include counting events, creating a one-shot or frequency output, and measuring frequency input. They can also be used to set the duty cycle, frequency, and output polarity of the output pulse.

These counter/timers can be cascaded. Cascade 2 counter/timers internally through software. Cascade 3 or 4 counter/timers externally on a screw terminal accessory.

PCI/ISA/PCMCIA

12-bit resolution

- Throughput of up to 225kS/s or 400kS/s

- Digital I/O scanning speeds of up to 3MHz

- 16 single-ended or 8 differential analog inputs

- 23 digital I/O lines

- 2 analog outputs (KPCI-3102) and -3104 only)

- 4 counter/timers

- Low gain (1, 2, 4, 8)

- Pre-, post-, and abouttriggering

- 1024-location channel-gain queue

- 32-bit DriverLINX drivers plus a suite of bundled software including ExceLINX, VisualSCOPE, TestPoint, and LabVIEW drivers

www.keithley.com

### KPCI-3101 KPCI-3102 KPCI-3103 KPCI-3104

### **Ordering Information**

| KPCI-3101 | Low-gain,<br>multifunction,<br>225kS/s, PCI-bus<br>board                        |

|-----------|---------------------------------------------------------------------------------|

| KPCI-3102 | Low-gain,<br>multifunction,<br>225kS/s, PCI-bus<br>board with Analog<br>outputs |

| KPCI-3103 | Low-gain,<br>multifunction,<br>400kS/s, PCI-bus<br>board                        |

| KPCI-3104 | Low-gain,<br>multifunction,<br>400kS/s, PCI-bus<br>board with Analog<br>outputs |

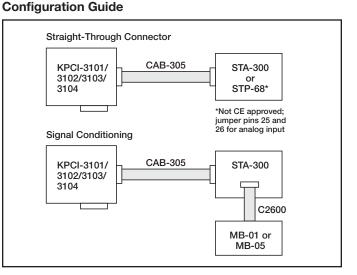

#### ACCESSORIES AVAILABLE

| C2600                                                      | STA-300 to MB-01 Cable                       |  |  |

|------------------------------------------------------------|----------------------------------------------|--|--|

| CAB-305                                                    | KPCI-3101/3102/3103/3104 to STA-300, 68-pin, |  |  |

|                                                            | 2-meter, Shielded Cable                      |  |  |

| STA-300                                                    | Screw Terminal Accessory                     |  |  |

| STP-68                                                     | Screw Terminal Panel (not CE approved)       |  |  |

| MB-01*                                                     | 16-Channel Direct-Connection Module          |  |  |

|                                                            | Mounting Rack                                |  |  |

| MB-05*                                                     | 8-Channel Direct-Connection Module Mounting  |  |  |

|                                                            | Rack                                         |  |  |

| TESTPOINT                                                  | TestPoint Software Package                   |  |  |

| *Signal conditioning modules for the MB-01_MB-02_and MB-05 |                                              |  |  |

\*Signal conditioning modules for the MB-01, MB-02, and MB-05 can be found in the Signal Conditioning and Accessories section.

### Physical and Environmental Specifications

PHYSICAL:

- Dimensions: 8.5 inches (length) by 4.2 inches (width). I/O Connector: 68 pin Amp (#749621-7).

- **CERTIFICATION AND COMPLIANCE:** FCC Class A verified; will not compromise FCC compliance of host computer CE.

- **COMPLIANCE:** Conforms to European Union directive 89/336/EEC (EMC directive), EN55022, and EN50082-1. (Product is CE marked.)

ENVIRONMENTAL:

**Operating Temperature Range:** 0°C to 70°C. **Storage Temperature Range:** -25°C to 85°C. **Relative Humidity:** To 95%, noncondensing.

# 225/400kHz, 12-Bit, Low Gain Analog I/O Boards

### **Features Summary**

| ANALOG INPUT   | -            |            |                   |               |

|----------------|--------------|------------|-------------------|---------------|

| Board          | Channels     | Resolution | n Input Rang      | es            |

| KPCI-3101/3102 | 16 SE/8 Diff | 12 bits    | ±1.25, 2.5, 5, 1  | 10 V          |

|                |              |            | 0-1.25, 2.5, 5,   | 10 V          |

| KPCI-3103/3104 | 16 SE/8 Diff | 12 bits    | ±1.25, 2.5, 5, 1  | 10 V          |

|                |              |            | 0-1.25, 2.5, 5, 1 | 10 V          |

| ANALOG OUTPL   | JTS          |            |                   |               |

| Board          | Channels     | Resolution | Output Ranges     | Counter/Timer |

| KPCI-3101/3103 | 0            | N/A        | N/A               | 4             |

| KPCI-3102/3104 | 2            | 16 bits    | ±10 V             | 4             |

### **Analog Inputs**

|                                         | KPCI-3101/3102                                                                                                 | KPCI-3103/3104                                                     |  |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|

| Number of analog input channels         |                                                                                                                |                                                                    |  |

| Single-ended/pseudo-differential        | 16                                                                                                             | 16                                                                 |  |

| Differential                            | 8                                                                                                              | 8                                                                  |  |

| Resolution                              | 12 bits                                                                                                        | 12 bits                                                            |  |

| Channel-gain list                       | 1024 locations                                                                                                 | 1024 locations                                                     |  |

| Input FIFO size                         | 1024 locations                                                                                                 | 1024 locations                                                     |  |

| Input gains                             | 1, 2, 4, 8                                                                                                     | 1, 2, 4, 8                                                         |  |

| Input range                             |                                                                                                                |                                                                    |  |

| Bipolar                                 | $\pm 10, \pm 5, \pm 2.5, \pm 1.25$ V                                                                           | $\pm 10, \pm 5, \pm 2.5, \pm 1.25$ V                               |  |

| Unipolar                                | 0–10, 5, 2.5, 1.25 V                                                                                           | 0–10, 5, 2.5, 1.25 V                                               |  |

| Drift<br>Zero                           | $\pm 30\mu V + (+20\mu V*Gain)/^{\circ}C$                                                                      | $\pm 30\mu V + (+20\mu V^*Gain)/^{\circ}C$                         |  |

| Gain                                    | $\pm 30 \mu\text{v} + (\pm 20 \mu\text{v} \cdot \text{Gall})/\text{C}$<br>$\pm 30 \text{ppm}/^{\circ}\text{C}$ | $\pm 30 \mathrm{ppm}^{\circ}$ C                                    |  |

| Input impedance                         | 100 MΩ, 10 pF, Off                                                                                             | 100 MΩ, 10 pF, Off                                                 |  |

| input impedance                         | $100 \text{ M}\Omega$ , $100 \text{ pF}$ , On                                                                  | $100 \text{ M}\Omega_2$ , 10 pF, On<br>100 M $\Omega$ , 100 pF, On |  |

| Input bias current                      | ±20 nA                                                                                                         | ±20 nA                                                             |  |

| Common mode voltage                     | ±11 V maximum (operational)                                                                                    | ±11 V maximum operational                                          |  |

| Maximum input voltage                   | $\pm 35$ V maximum (protection)                                                                                | ±35 V maximum (protection)                                         |  |

| Channel acquisition time                | 3 μs                                                                                                           | 1 μs                                                               |  |

| A/D conversion time                     | 4.44 μs                                                                                                        | 2.5 µs                                                             |  |

| Accuracy                                | 1 · · ·                                                                                                        |                                                                    |  |

| Nonlinearity (integral)                 | ±1.0 LSB                                                                                                       | ±1.0 LSB                                                           |  |

| Differential nonlinearity               | $\pm 0.5$ LSB (no missing codes)                                                                               | $\pm 0.5$ LSB (no missing codes)                                   |  |

| System noise                            | 0.3 LSB rms                                                                                                    | 0.3 LSB rms                                                        |  |

| Channel-to-channel offset               | $\pm 40.0 \ \mu V$                                                                                             | $\pm 40.0 \mu\text{V}$                                             |  |

| Clocking and trigger input              |                                                                                                                |                                                                    |  |

| Maximum A/D pacer clock                 |                                                                                                                |                                                                    |  |

| Single analog input throughput          | 225 kS/s @ 0.03% accuracy                                                                                      | 400 kS/s @ 0.03% accuracy                                          |  |

| Multiple analog input throughput        | 160 kS/s @ 0.03% accuracy                                                                                      | 300 kS/s @ 0.03% accuracy                                          |  |

| Multiple analog input throughput        | 225 kS/s @ 0.05% accuracy                                                                                      | 400 kS/s @ 0.05% accuracy                                          |  |

| Single digital input channel            | 3 MS/s                                                                                                         | 3 MS/s                                                             |  |

| Minimum A/D pacer clock throughput      | 1.2 S/s                                                                                                        | 1.2 S/s                                                            |  |

| External A/D sample clock               |                                                                                                                |                                                                    |  |

| Minimum pulse width                     | 100 ns (high); 100 ns (low)                                                                                    | 100 ns (high); 100 ns (low)                                        |  |

| Maximum frequency (analog inputs)       | 225 kHz                                                                                                        | 400 kHz                                                            |  |

| Maximum frequency (digital inputs only) | 3 MHz                                                                                                          | 3 MHz                                                              |  |

| External digital (TTL) trigger          |                                                                                                                |                                                                    |  |

| High-level input voltage                | 2.0 V minimum                                                                                                  | 2.0 V minimum                                                      |  |

| Low-level input voltage                 | 0.8 V maximum                                                                                                  | 0.8 V maximum                                                      |  |

| Minimum pulse width                     | 100 ns (high); 100 ns (low)                                                                                    | 100 ns (high); 100 ns (low)                                        |  |

1.888.KEITHLEY (U.S. only)

www.keithley.com

### KPCI-3101 KPCI-3102 KPCI-3103 KPCI-3104

## 225/400kHz, 12-Bit, Low Gain Analog I/O Boards

### **Analog Outputs**

|                                  | KPCI-3102                         | KPCI-3104                         |  |

|----------------------------------|-----------------------------------|-----------------------------------|--|

| Number of analog output channels | 2 (voltage output)                | 2 (voltage output)                |  |

| Resolution                       | 16 bits                           | 16 bits                           |  |

| Output range                     | ±10 V                             | ±10 V                             |  |

| Error: Gain                      | $\pm 32$ LSB + Reference          | $\pm 32$ LSB + Reference          |  |

| Zero                             | Software adjustable to 0          | Software adjustable to 0          |  |

| Current output                   | ±5 mA maximum                     | ±5 mA maximum                     |  |

| Output impedance                 | 0.3 Ω typical                     | 0.3 Ω typical                     |  |

| Capacitive drive capability      | 0.001 µF (no oscillations)        | 0.001 µF (no oscillations)        |  |

| Nonlinearity (integral)          | ±16 LSB                           | ±16 LSB                           |  |

| Differential linearity           | ±8 LSB (monotonic)                | ±8 LSB (monotonic)                |  |

| Protection                       | Short circuit to<br>Analog Common | Short circuit to<br>Analog Common |  |

| Power-on voltage                 | 0 V ±10 mV                        | 0 V ±10 mV                        |  |

| Settling time to 0.01% of FSR    | 50 µs, 20 V step;                 | 50 µs, 20 V step                  |  |

|                                  | 10.0 µs, 100 mV step              | 10.0 µs, 100 mV step              |  |

| Slew rate                        | 2 V/µs                            | 2 V/µs                            |  |

### Digital I/O

KPCI-3101, KPCI-3102, KPCI-3103, KPCI-3104 Specifications

|                                                            | Port A                                         | Port B                                         | Port C                                        |

|------------------------------------------------------------|------------------------------------------------|------------------------------------------------|-----------------------------------------------|

| Number of lines                                            | 8 bidirectional                                | 8 bidirectional                                | 7 bidirectional                               |

| Inputs                                                     |                                                |                                                |                                               |

| High-level input voltage                                   | 2.0 V minimum                                  | 2.0 V minimum                                  | 2.0 V minimum                                 |

| Low-level input voltage                                    | 0.8 V maximum                                  | 0.8 V maximum                                  | 0.8 V maximum                                 |

| High-level input current                                   | 3 µA                                           | 3 μA 3 μA                                      |                                               |

| Low-level input current                                    | $-3 \mu A$                                     | $-3 \mu A$                                     | $-100 \mu\text{A}$                            |

| Maximum internal pacer clock rate (single digital channel) | 3 MHz                                          | 3 MHz                                          | 3 MHz                                         |

| Outputs                                                    |                                                |                                                |                                               |

| Output driver high voltage                                 | 2.4 V minimum<br>( $I_{OH} = -15 \text{ mA}$ ) | 2.4 V minimum<br>( $I_{OH} = -15 \text{ mA}$ ) | 2.4  V  minimum<br>$(I_{OH} = -4 \text{ mA})$ |

| Output driver low voltage                                  | 0.5  V  maximum<br>$(I_{OL} = 12 \text{ mA})$  |                                                |                                               |

### Counter/Timer

NUMBER OF COUNTER/TIMER CHANNELS: 4. CLOCK INPUTS:

- High-Level Input Voltage: 2.0V minimum.

- Low-Level Input Voltage: 0.8V maximum.

- Minimum Pulse Width: 100ns (high); 100ns (low).

Maximum Frequency: 5.0MHz. GATE INPUTS:

- High-Level Input Voltage: 2.0V minimum.

- Low-Level Input Voltage: 0.8V maximum.

- Minimum Pulse Width: 100ns (high); 100ns (low).

COUNTER OUTPUTS:

Output Driver High Voltage: 2.0V minimum ( $I_{OH} = -15mA$ ); 2.4V minimum ( $I_{OH} = -3mA$ ). Output Driver Low Voltage: 0.5V maximum ( $I_{OL} = -24mA$ ); 0.4V maximum ( $I_{OL} = -12mA$ ).

### **Connector Pin Assignments**

The analog input, analog output, digital input, and digital output connections are made with a 68-pin, subminiature D connector at the rear of the computer.

| Analog Input 0             | 68 |  |  | 34 | Analog Input 1               |

|----------------------------|----|--|--|----|------------------------------|

| Analog Input 8/0 Return    | 67 |  |  | 33 | Analog Input 9/1 Return      |

| Analog Input 2             | 66 |  |  | 32 | Analog Input 3               |

| Analog Input 10/2 Return   | 65 |  |  | 31 | Analog Input 11/3 Return     |

| Analog Input 4             | 64 |  |  | 30 | Analog Input 5               |

| Analog Input 12/4 Return   | 63 |  |  | 29 | Analog Input 13/5 Return     |

| Analog Input 6             | 62 |  |  | 28 | Analog Input 7               |

| Analog Input 14/6 Return   | 61 |  |  | 27 | Analog Input 15/7 Return     |

| DAC0 Reference             | 60 |  |  | 26 | Amp Low                      |

| DAC1 Reference             | 59 |  |  | 25 | Analog Ground                |

| Analog Output 0            | 58 |  |  | 24 | Analog Output 1              |

| Analog Output 0 Return     | 57 |  |  | 23 | Analog Output 1 Return       |

| External A/D Trigger       | 56 |  |  | 22 | External A/D Sample Clock In |

| Digital Ground             | 55 |  |  | 21 | Digital Ground               |

| Digital I/O Port C, Line 0 | 54 |  |  | 20 | Digital I/O Port C, Line 1   |

| Digital I/O Port C, Line 2 | 53 |  |  | 19 | Digital I/O Port C, Line 3   |

| Digital I/O Port C, Line 4 | 52 |  |  | 18 | Digital I/O Port C, Line 5   |

| Digital I/O Port C, Line 6 | 51 |  |  | 17 | Digital Ground               |

| Digital I/O Port A, Line 0 | 50 |  |  | 16 | Digital I/O Port A, Line 1   |

| Digital I/O Port A, Line 2 | 49 |  |  | 15 | Digital I/O Port A, Line 3   |

| Digital I/O Port A, Line 4 | 48 |  |  | 14 | Digital I/O Port A, Line 5   |

| Digital I/O Port A, Line 6 | 47 |  |  | 13 | Digital I/O Port A, Line 7   |

| Digital I/O Port B, Line 0 | 46 |  |  | 12 | Digital I/O Port B, Line 1   |

| Digital I/O Port B, Line 2 | 45 |  |  | 11 | Digital I/O Port B, Line 3   |

| Digital I/O Port B, Line 4 | 44 |  |  | 10 | Digital I/O Port B, Line 5   |

| Digital I/O Port B, Line 6 | 43 |  |  | 9  | Digital I/O Port B, Line 7   |

| Digital Ground             | 42 |  |  | 8  | Digital Ground               |

| User Clock Input 0         | 41 |  |  | 7  | User Clock Input 1           |

| User Counter Output 0      | 40 |  |  | 6  | User Counter Output 1        |

| External Gate 0            | 39 |  |  | 5  | External Gate 1              |

| External Gate 2            | 38 |  |  | 4  | External Gate 3              |

| User Counter Output 2      | 37 |  |  | 3  | User Counter Output 3        |

| User Clock Input 2         | 36 |  |  | 2  | User Clock Input 3           |

| Power Ground               | 35 |  |  | 1  | +5V Output @ 1A              |

|                            |    |  |  |    |                              |

When using STP-68, make a connection between Amp Low and Analog Ground (W1 jumper on STA-300).

www.keithley.com